Design of SDRAM controller based on AMBA-AHB bus

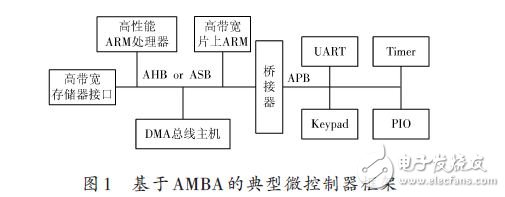

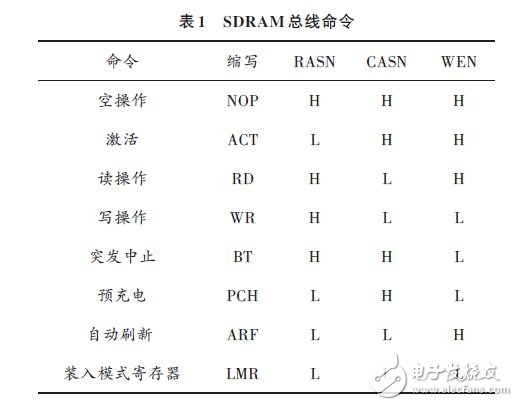

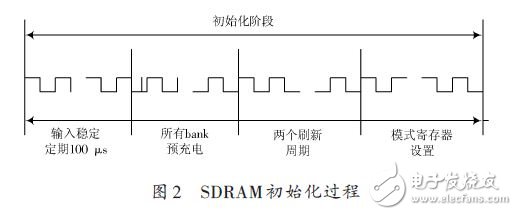

0 Preface With the development of large-scale integrated circuits and high-speed, low-power, high-density storage technologies, SDRAM dynamic memories have become the mainstream of PC memory due to their large capacity, high speed, and low price. However, the internal control logic of the SDRAM memory is very complicated, and the timing requirements are also very strict. Therefore, it is necessary to design a special SDRAM controller to realize the system access to the SDRAM. The memory controller is the interface between the AMBA-AHB bus and the off-chip storage device in the embedded microprocessor, and completes the data transmission of the bus master device (CPU or DMA) and off-chip storage device (SDRAM or SRAM), its function and performance. It determines the type of external memory supported by the embedded microprocessor and the access speed of the external memory, which in turn determines the processing speed of the entire embedded system. The AMBA bus specification has become the standard for embedded on-chip bus in microprocessors. The design is based on the AMBA bus standard. The storage controller IP supporting the common memory types of embedded systems has great practical significance. 1 AMBA bus introduction A typical AMBA bus-based microcontroller architecture is shown in Figure 1. It contains an AHB (Advanced High-Performance Bus) or ASB bus as a system skeleton that enables large amounts of data communication between the CPU or DMA module and off-chip memory to achieve large bandwidth. In addition, there is a bridge on this high-performance bus to connect low-bandwidth APBs, while most of the system peripherals are connected to the APB. Users can independently design microprocessors and peripheral IPs based on this specification, which improves system development efficiency and module reusability [6]. Among them, the AHB bus is a high-performance bus supporting multi-bus masters for high-performance, high-clock-frequency systems, which ensures an effective connection between the processor and off-chip memory. A complete AHB transmission process can be divided into an address transmission phase and a data transmission phase, an address transmission phase transmits an address and a control signal, and a data transmission phase transmits a read-write data and a response signal. The AHB bus supports pipeline transmission, which means that the next address transmission phase can be performed simultaneously in the previous data transmission phase, and different transmission phases can be overlapped to improve the data processing speed of the system. 2 SDRAM working principle SDRAM is a high-speed and high-capacity synchronous dynamic memory. Compared with static memory such as SRAM, it has the advantages of large capacity, high speed and low price. It is a commonly used data memory in image processing. However, due to the particularity of the SDRAM memory structure, it is necessary to continuously perform precharge, refresh, and the like on the SDRAM to keep data from being lost. The internal operation of the SDRAM is implemented by bus commands, which are jointly generated by the RASN, CASN, and WEN signals, as shown in Table 1 (H indicates high level and L indicates low level). After the SDRAM is powered up, it must be initialized in a certain way. The memory does not accept any commands other than NOP for 100 μs after power-up stabilization. After 100 μs, the precharge command [8] is issued to all banks of the SDRAM through the controller, causing all banks of the SDRAM to enter the standby state. After that, two automatic refresh operations are continuously performed on the SDRAM, so that the internal refresh of the SDRAM chip and the counter enter a normal running state. After the two refresh cycles are completed, the SDRAM mode register (Mode Register) is operated. The mode register is used to determine which operating mode the SDRAM will operate. The entire initialization process is shown in Figure 2. Down Tube Battery,Ebike Lithium Battery,24V Bottle Battery,24V Electric Bicycle Battery Changxing Deli Technology Co., Ltd. , https://www.delipowers.com