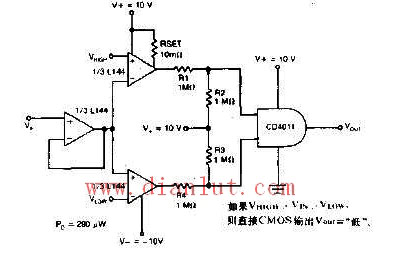

Dual Extreme Low Power Detector Circuit Diagram

Dual extreme low power detector circuit The figure shows the circuit diagram of the dual-limit low-power detector. The detector uses a three operational amplifier in the L144 and a CD4011 CMOS NAND gate to form a very low power voltage monitor. If the input voltage Vin is higher than Vhigh or lower than Vlow the output will be logic "high". If the input is within this limit, the output is logic "low". The 1MΩ resistors R1, R2, R3, and R4 turn the bipolar wobble placed within 10V into a wobble within 0~10V to be compatible with ground-referenced CMOS logic. 2-in-1 Tablet, tablet with keyboard, android tablet with case tablet with pen, mini laptop C&Q Technology (Guangzhou) Co.,Ltd. , https://www.gzcqteq.com